# Comparison Between Simulations and Measurements of Large Signal and Nonlinear Noise Behaviors of MMIC Analog Frequency Divider by Two

B. Branger, E. LaPorte, J. C. Nallatamby, M. Prigent, *Member, IEEE*, and L. LaPierre

**Abstract**—For the first time, the large signal and nonlinear noise behaviors of an analog frequency divider has been fully simulated and measured: comparisons between predicted and measured results of this circuit are given. The circuit designed is a monolithic microwave integrated circuit (MMIC) *X*-band 8.2–4.1-GHz analog frequency divider by two. The large signal analysis relies on the open-loop method extended to synchronous systems. The simulation of noise behavior of such a circuit has been performed by means of the nonlinearities conversion matrices and noise generators correlation matrices analysis.

## I. INTRODUCTION

**N**OWADAYS, communication systems require sophisticated frequency generation circuits such as phase-locked loops and frequency synthesizers. Analog frequency dividers offer the possibility of being integrated with other electronic functions in the same GaAs Chip. Moreover, the noise performances are supposed to be better than those of digital ones [1]. Consequently, frequency division is a key function of these circuits [2] and can be performed in a digital or an analog way. To reach high performance, the monolithic microwave integrated circuit (MMIC) technology seems efficient. The aim of this letter is to present the comparison between simulations and measurement of a *X*-band (8.2–4.1 GHz) analog frequency divider by two, which is the part of frequency generation circuit for a satellite load of telemeasurement. This circuit was processed by using a qualified MESFET 0.7- $\mu$ m high-power technology. However, to simulate such a circuit, CAD tools can present an important deficit, mainly in noise simulation. So, we have developed specific design methods to calculate the large-signal regime [3] and the noise performance of these potentially unstable circuits. To our knowledge, it is the first-reported analysis of noise performances of a frequency divider. For each kind of analysis, some comparisons between simulated and measured results are presented.

## II. DESIGN AND LARGE SIGNAL ANALYSIS OF THE ANALOG DIVIDER BY TWO

The working principle of the analog divider relies on a closed loop in which the output signal at the divided frequency

Manuscript received November 8, 1996. This work was supported by Alcatel Espace (C. Tronche).

B. Branger, E. LaPorte, J. C. Nallatamby, and M. Prigent are with I.R.C.O.M.–C.N.R.S., 19100 Brive, France.

L. LaPierre is with C.N.E.S., 31055 Toulouse Cedex, France.

Publisher Item Identifier S 1051-8207(97)03322-9.

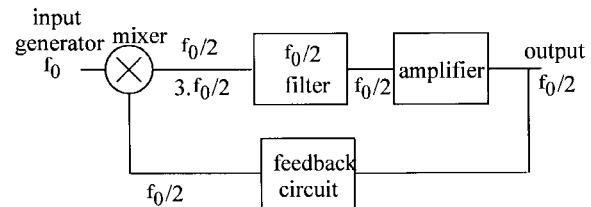

Fig. 1. Diagram of frequency divider by two.

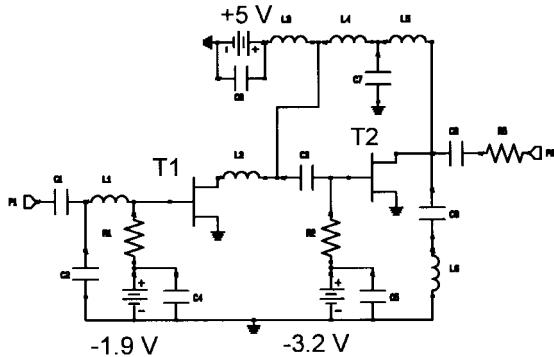

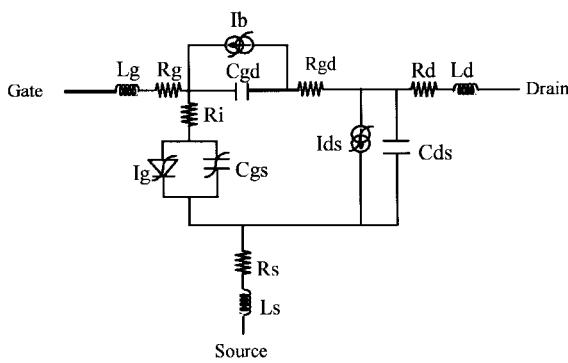

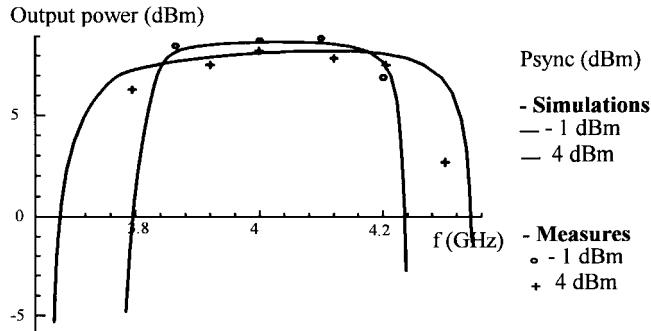

is fed back and mixed with the external signal to produce a lower sideband at the output frequency, which will be filtered and amplified. In addition, this closed-loop circuit may oscillate at the divided frequency without external generator. The block diagram of such a circuit is shown in Fig. 1. A phase relation must exist between the injection signal and the output signal in order to get a synchronous stable regime. The divider, whose electrical scheme is presented in Fig. 2, is composed of an input buffer amplifier providing the required power and matching to the working of a second active stage, which behaves as a frequency divider at  $f_0/2 = 4.1$  GHz. The large-signal design of this circuit is based on the open-loop method extended to synchronous systems detailed in [3]. The large-signal model of the transistor is presented in Fig. 3 [4]. Without any injected signal, the analog frequency divider by two acts as a free-running oscillator working at the frequency of 4.1 GHz. This way, the output power versus the output frequency is measured and simulated for different input powers, equal to  $-1$  and  $4$  dBm. The results are presented in Fig. 4. A good accuracy is also obtained between the simulated and experimental results. Note that a flat power of  $8$  dBm on about the whole synchronized band is obtained for a  $-1$ -dBm input power. A 12% synchronized bandwidth around the central frequency for an input power of  $4$  dBm is obtained.

## III. NONLINEAR NOISE ANALYSIS OF THE ANALOG DIVIDER BY TWO

The noise behavior of the divider is perturbed by internal noise sources (additive noise) and by the amplitude and phase noise spectra of the synchronizing generator. The simulation technique we have implemented allows to take into account both noise sources. This simulation method is based on conversion matrix formalism [5], [6]: it consists of representing the active device nonlinearities by their conversion matrices. Moreover, in this analysis, noise generators are depicted by

Fig. 2. Electrical scheme of the frequency divider.

Fig. 3. Nonlinear model of the transistor.

Fig. 4. Output power versus synchronized bandwidth.

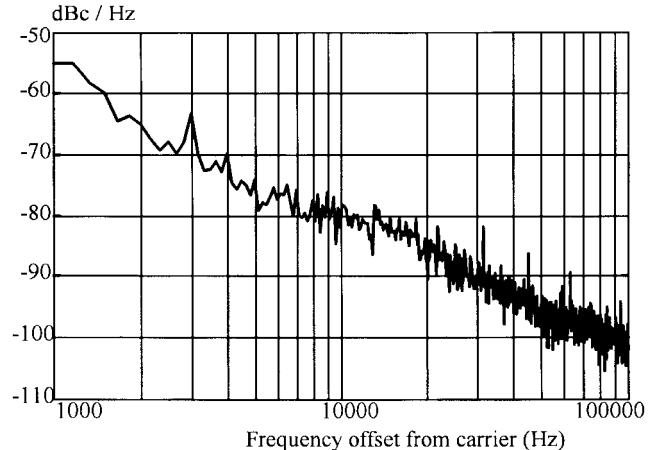

their correlation matrices. To perform such an analysis, the divider in large signal steady-state regime must be perfectly known. Moreover, the low-frequency noise sources of the transistor and the noise spectrum of synchronizing generator must be measured and introduced into CAD tool to calculate phase noise spectrum. The transistor low-frequency noise model used in the simulation is the classical model, with only one voltage-equivalent noise generator at the input of the transistor. Its spectral density has a  $k/f$  law with a constant  $k = 9.58e - 10$ . To operate in the frequency divider regime, the divider has been synchronized by an external source at frequency  $f_0$ , which varies in the locking band [7.6–8.4 GHz] and presents the phase noise spectrum density of Fig. 5. For a synchronized input power of 2 dBm, the output phase noise spectrum has been simulated and measured in the whole synchronized bandwidth. For the simulation,

Fig. 5. Phase noise spectrum of the synchronizing oscillator.

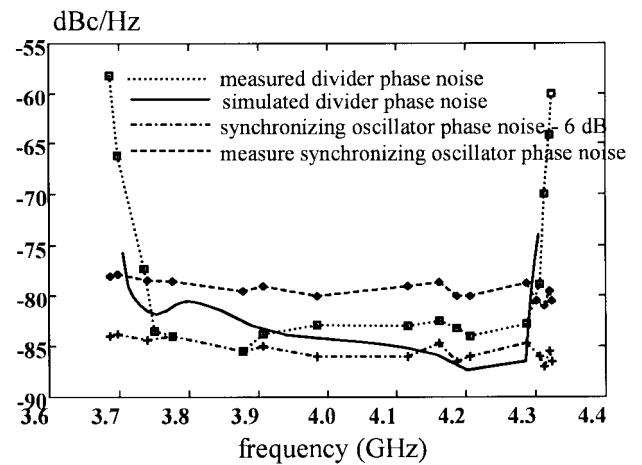

Fig. 6. Simulated and measured phase noise spectra against the locking band.

both divider low-frequency noise and synchronizing oscillator phase noise spectrum have been taken into account. These phase noise spectrum results at 10 kHz offset from the carrier versus synchronized frequency are given in Fig. 6. The input phase noise minus the reduction of 6 dB due to the division row is also reported in this figure. Note that the copy of this spectrum is not being kept constant in the whole locking range, as is obtained with a simple model [7]. At the edges of the synchronized band, the noise increases due to instability of the divider. To the best of our knowledge, these are the first simulations and measurements carried out over the whole synchronization band by taking into account the complete circuit.

#### IV. CONCLUSION

This letter presents the comparison between simulations and measurements of large signal and noise behavior of a MMIC X-band 8.2–4.1-GHz analog frequency divider by two. This device has been designed with large-signal analysis using the open-loop method extended to the synchronous circuits to permit us obtaining 12% synchronized bandwidth for an input power of 2 dBm and a flat output of 9 dBm. For the first time

published, the phase noise spectrum was compared with good accuracy between simulated and measured ones.

#### ACKNOWLEDGMENT

The authors would like to thank H. Kimouche for the phase-noise measurements and L.A.A.S for the low-frequency noise measurements.

#### REFERENCES

- [1] M. R. McClure, "Residual phase noise of digital frequency dividers," *Microwave J.*, Mar. 1992.

- [2] M. Bourford, "Selection of frequency dividers for microwave PLL applications," *Microwave J.*, pp. 159-167, Nov. 1990.

- [3] J. C. Sarkissian, M. Camiade, P. Savary, A. Suarez, and R. Quéré, "A 60 GHz HEMT MMIC analog frequency dividers by two," *IEEE J. Solid State Circuits*, vol. 30, no. 10, Oct. 1995.

- [4] J. P. Teyssier, J. P. Viaud, and R. Quéré, "A new nonlinear  $I(V)$  model for FET devices including breakdown effects," *IEEE Microwave Guided Wave Lett.*, vol. 4, pp. 104-107, Apr. 1994.

- [5] J. M. Paillot, J. C. Nallatamby, M. Hessane, R. Quéré, M. Prigent, and J. Rousset, "A general program for steady-state and F.M. noise analysis of microwave oscillators," in *1990 IEEE MTT-S Int. Microwave Symp. Dig.*, pp. 1287-1290.

- [6] M. Prigent, J. C. Nallatamby, E. Ngoya, R. Quéré, and J. Obregon, "Simulation techniques of non linear circuit dynamic behavior," *Anal. Telecomm.*, vol. 51, no. 9-10, pp. 541-552, Oct. 1996.

- [7] O. Llopis, H. Amine, M. Gayral, J. Graffeuil, and J. F. Sautereau, "Analytical model of noise in an analog frequency divider," in *1993 IEEE MTT-S Int. Microwave Symp. Dig.*, pp. 1033-1036.